desarrollo:hardware:ciaa_freescale:ethernet_freescale

Tabla de Contenidos

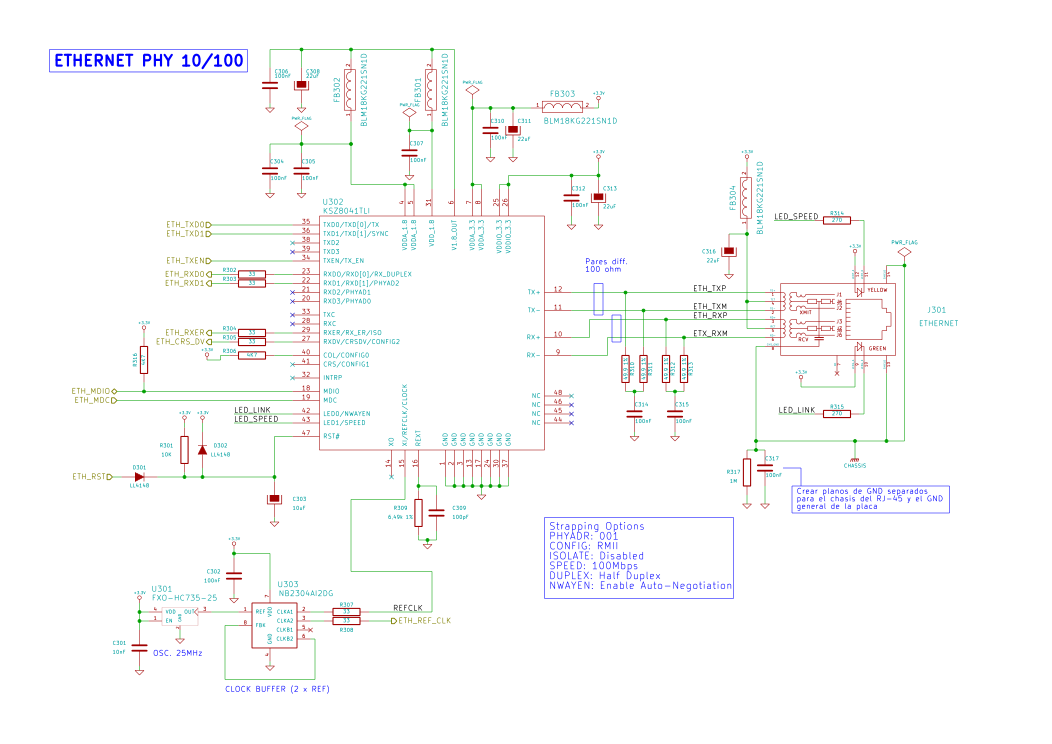

CIAA-FSL: Interfaz Ethernet

Diagrama Esquemático

Características

- Transceiver: Micrel KSZ8041TLI

- Compatible con el estándar IEEE 802.3u.

- Full-Duplex 10Mbps/100Mbps (10Base-T/100Base-TX).

- Diseño CMOS de bajo consumo, menor a 180 mW.

- Interfaz MII/RMII/SMII hacia la CPU.

- Salidas programables para LEDs de link, actividad y velocidad.

- Jack RJ45: Pulse J0011D01BNL

- Transformador y choque de modo común integrados.

- 2 leds (verde y amarillo).

- Oscilador de 25 MHz: Fox Electronics FXO-HC735-25

- Clock Buffer: ON Semiconductor NB2304AI2

- Delay cero entre entrada y salida

- Salida 2xREF

Descripción

- El modo de conexión utilizado entre el K60 y el transceiver es RMII, para el cual es necesario un clock de 50 MHz.

- Se utiliza un oscilador de 25 MHz conectado a un buffer con dos salidas con el doble de frecuencia que la de referencia, una se conecta al transceiver y la otra al K60.

- El shield del conector RJ45 se conecta al chassis general de la placa que a su vez está conectado al terminal de puesta a tierra.

- El shield del conector RJ45 está conectado a la masa del circuito a través de un capacitor de 100 nF y un resistor de 1 Mohm. Este circuito permite un camino controlado para la descarga electrostática (ESD), captada por el shield, hacia GND. Como recomienda la Nota de Texas (citada abajo), estos componentes pueden cambiarse por un ferrite o un resistor de 0 ohm, según los resultados del test de EMC.

Referencias

Datasheets de componentes importantes

desarrollo/hardware/ciaa_freescale/ethernet_freescale.txt · Última modificación: 2014/09/22 17:21 por 37.228.105.244