Tabla de Contenidos

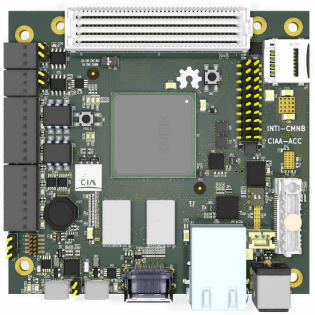

CIAA-ACC

Computadora industrial abierta para aplicaciones de Alto Costo Computacional

Resumen

Este proyecto está orientado al desarrollo de una computadora industrial en la modalidad de hardware libre que soporte aplicaciones de alto costo computacional, como son los sistemas de visión y procesamiento de imágenes y el manejo de pantallas de alta resolución, y que sea capaz de correr sistemas operativos de tipo Linux. En particular, el presente proyecto abordará al menos tres campos del conocimiento que son centrales para el desarrollo de sistemas digitales complejos:

- Análisis, selección y utilización a nivel chip de procesadores o circuitos lógicos programables que brinden la capacidad de cómputo y las arquitecturas requeridas.

- Análisis, selección e implementación de sistemas operativos compatibles con entornos de tipo Linux, que sean acordes a sistemas industriales de tiempo real.

- Técnicas de diseño de circuitos impresos que permitan soportar la tasa de datos requerida para aplicaciones de este tipo, funcionando bajo condiciones industriales.

Este conocimiento no sólo redundará en beneficio de este proyecto y de quienes sean sus usuarios directos, sino que al trabajarse en la modalidad de hardware libre servirá también como referencia para el desarrollo nacional de otros sistemas embebidos similares.

Estado actual del proyecto (27/03/19)

Hay 10 PCBs armados por Asembli y otros tantos en Italia (ICTP) que fueron fabricados por EDADOC y que arrancaron sin problemas. INTI-CMNB y Emtech desarrollaron el software necesario para las pruebas básicas, esto está en el repo CIAA_ACC_Support. Falta documentar los pasos necesarios para la puesta en marcha y algunos detalles de hardware (jumpers por ejemplo). Hay 4 placas disponibles para su uso en manos de Ariel Lutenberg.

Etapa de estudio y selección

- Estudio y selección del sistema operativo. Alternativas para tiempo real y Linux.

- Estudio y selección de la arquitectura de Hardware. Alternativas de la arquitectura.

- Datos propuesta 1: Zynq UltraScale+ MPSoC (Xilinx)

- Datos propuesta 2: iMX6 (Freescale)

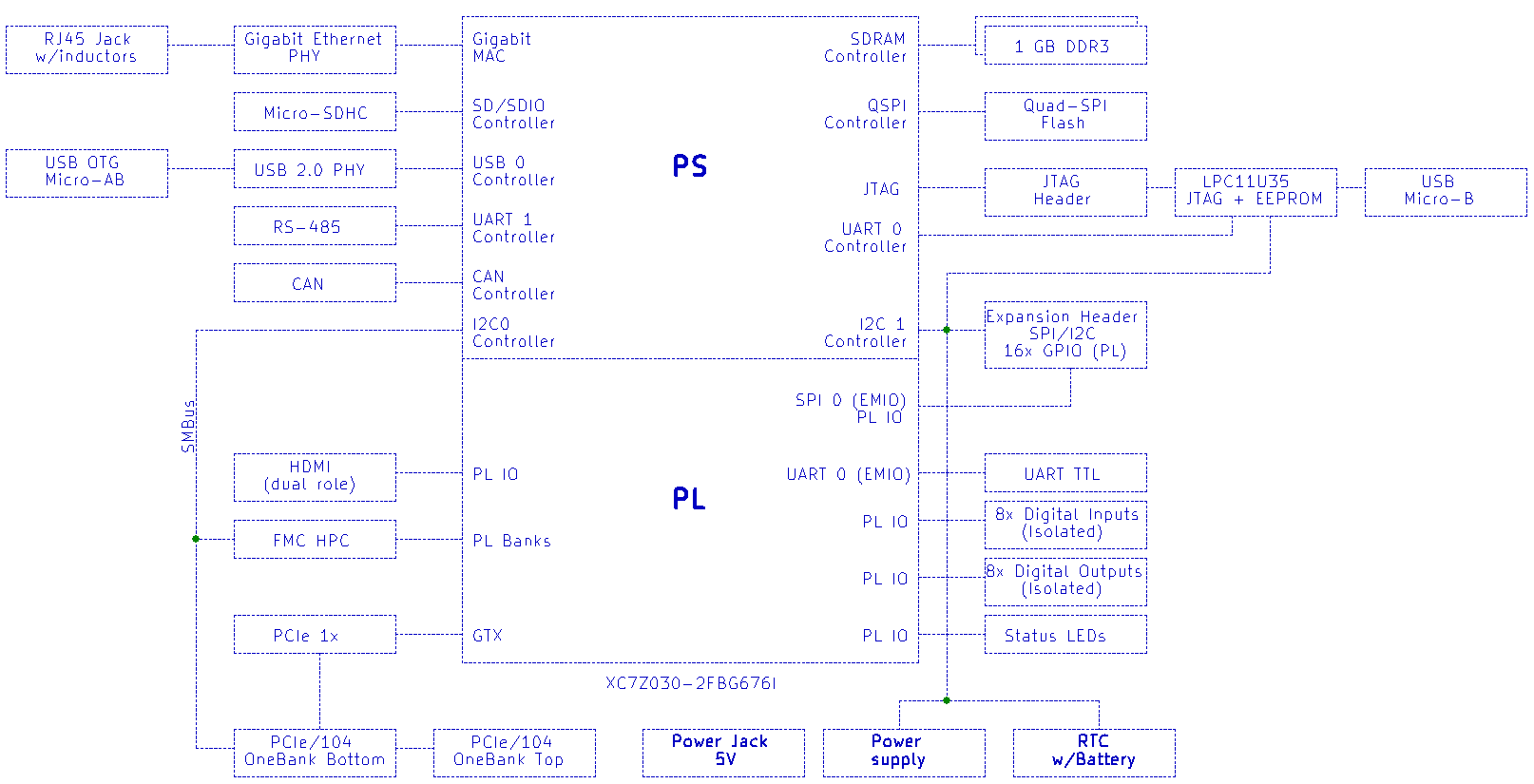

Diagrama en bloques

Nota 1: El bloque de las entradas analógicas se eliminó porque las líneas del ADC no pudieron ser ruteadas por falta de espacio en el PCB.

Nota 2: La entrada de la fuente de alimentación tuvo que dejarse en +5V porque las tensiones del procesador son muy bajas y no era coherente ni eficiente soportar +12V o +24V a la entrada.

Diagrama en bloques proyectado en Diciembre 2015.

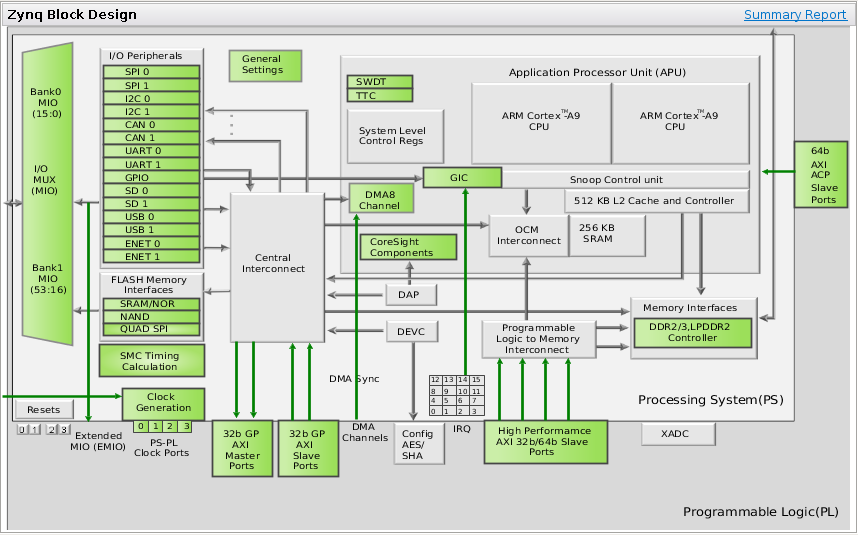

Para ilustrar las características del procesador seleccionado, se adjunta el diagrama del mismo tomado del software Vivado. Aquí pueden verse el procesador y todos los periféricos.

Lógica programable

La lógica programable del Zynq-7030 tiene las siguientes características:

| Part Number | XC7Z030 |

|---|---|

| Xilinx 7 Series Programmable Logic Equivalent | Kintex-7 FPGA |

| Programmable Logic Cells | 125K Logic Cells (~1.9M) |

| Look-Up Tables (LUTs) | 78,600 |

| Flip-Flops | 157,200 |

| Extensible Block RAM (# 36 Kb Blocks) | 1,060 KB (265) |

| Programmable DSP Slices (18×25 MACCs) | 400 |

| Peak DSP Performance (Symmetric FIR) | 593 GMACs |

| PCI Express (Root Complex or Endpoint) | Gen2 x4 |

| Analog Mixed Signal (AMS) / XADC | 2x 12 bit, MSPS ADCs with up to 17 Differential Inputs |

| Security | AES and SHA 256b for Boot Code and Programmable Logic Configuration, Decryption, and Authentication |

Diagramas Esquemáticos

Descripción de subsistemas e interfaces

EN PROCESO…

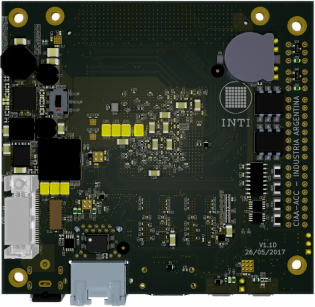

Placa del circuito impreso (PCB)

El proyecto completo de KiCAD puede bajarse del siguiente repositorio:

Acceso al repositorio de hardware en GitHub.

Hay varias versiones de gerber files en el repositorio:

- V1.1: Primera versión.

- V1.1B: Idéntica a la V1.1 pero con el agregado de números de identificación en cada capa.

- V1.1C: Idéntica a la V1.1B pero con el agregado de puntos fiduciales.

- V1.1D: Idéntica a la V1.1C pero con correcciones en la máscara antisoldante y la pasta.

- V1.1E: El fabricante EDADOC la generó a partir de la V1.1D, corrigiendo todos los puntos donde el clearance entre un agujero y una pista o entre un agujero y un pad era menor a 8.9 mils. También modificaron algunos anchos de pistas debido al cambio de un prepreg en el stackup. Esta es la versión lista para fabricar.

- V1.1F: Se cambiaron los componentes SMD que no aparecían en los pos files. Se corrigió la ubicación de los designators U45 y U47. Se cambió el texto IND. ARG. por DISEÑADO EN ARG.

Vistas 3D

Fotos y videos

Fabricación

Lista de Materiales (BOM)

Archivos Gerber

Demos y soporte básico

En el repositorio CIAA_ACC_Support están subidos los demos, y todos los archivos de soporte básico para comenzar a desarrollar el software. También está el manual de hardware escrito para el desarrollador de firmware y software.