desarrollo:hardware:ciaa_freescale:jtag_freescale

Tabla de Contenidos

CIAA-FSL: Debugger

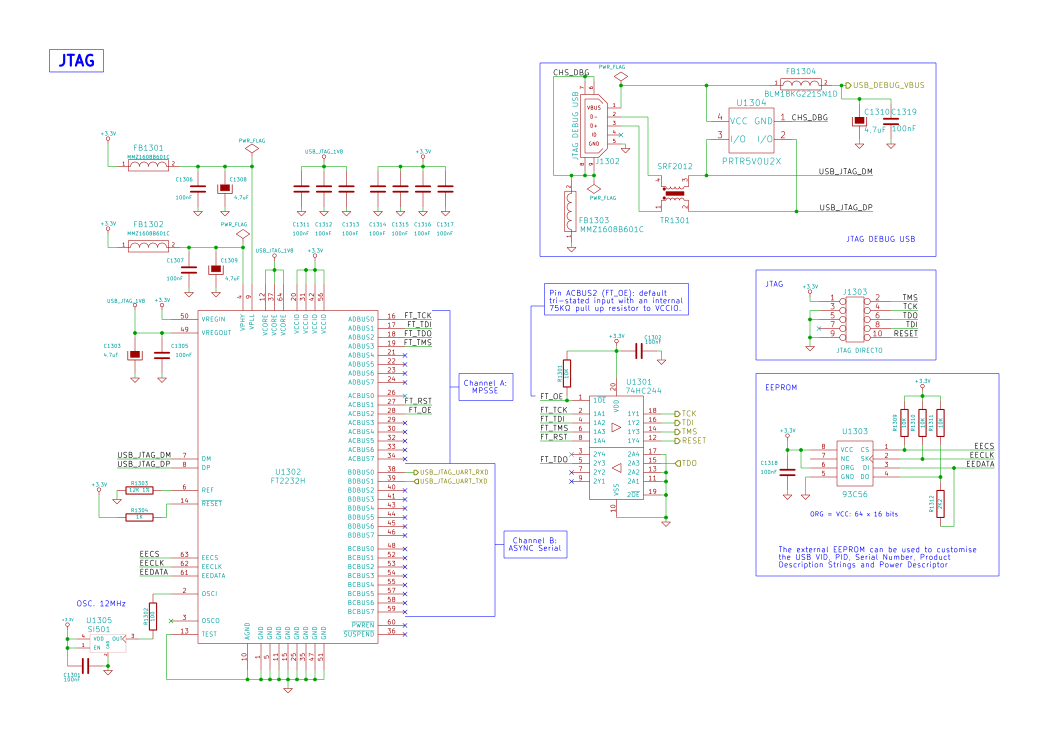

Diagrama Esquemático

Características

- Interfaz JTAG para debugger externo

- Conector SMD: HARWIN M50-3600542

- Debugger USB-JTAG con el chip FTDI CHIP FT2232HL

- Conector micro USB hembra de tipo AB SMT: Hirose ZX62-AB-5PA(11)

- Memoria EEPROM para el FT2232H: ATMEL AT93C46DN-SH-B

- Diodos TVS para protección contra ESD y transitorios: NXP PRTR5V0U2X,215

- Choque RF de modo común 90 ohm: Bourns SRF2012-900Y

- Buffer para desconectar el bus JTAG del FT2232 en caso de utilizar un debugger externo: NXP 74HC244PW,112

Descripción

- Tal como se indica en el documento de las características técnicas del hardware de la CIAA, la CIAA-FSL incluye un conector JTAG para debugging directo y un debugger JTAG USB integrado con el chip FT2232H.

- Para la interfaz JTAG USB se utilizó un conector micro USB hembra de tipo AB igual al de la interfaz USB OTG. Además, se incorporaron todas las protecciones para ESD y EMC.

- El buffer 74HC244 se puede deshabilitar en el caso de utilizar un debugger externo.

- La memoria EEPROM puede ser usada para almacenar la información de los descriptores USB: Vendor ID, Product ID, Serial Number, etc..

Referencias

Datasheets de componentes importantes

desarrollo/hardware/ciaa_freescale/jtag_freescale.txt · Última modificación: 2014/09/25 15:12 por ppezoimburu